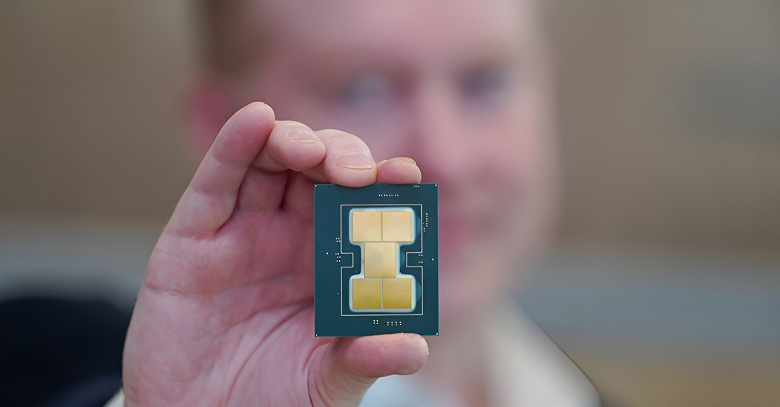

Intel showed the structure of Tiger Lake processors: a third of the chip is reserved for integrated graphics

Intel Tiger Lake mobile processors, which will be announced on September 2, were described in sufficient detail at the Intel Architecture Day 2020 event. Intel announced additional revelations about them at the Hot Chips conference. The image of the Tiger Lake crystal allowed us to understand what the developers’ priorities were when creating processors.